Verifying the True Jitter Performance of Clocks in High-Speed Digital Designs

- Measuring the Phase Noise

- Weighting the Phase Noise

- Integrating the Weighted Phase Noise

Application Note Overview

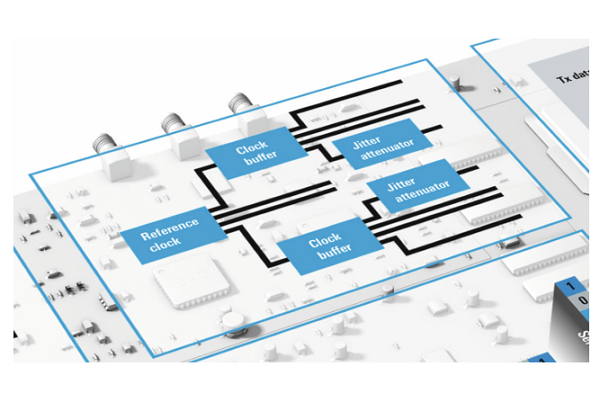

Measuring jitter for clocks in high-speed digital designs has become increasingly challenging. PCIe 5.0, for example, uses data rates of up to 32 gigatransfers per second (GT/s) with a corresponding jitter limit of 150 fs (RMS) for the reference clock. Data rates of 64 GT/s are introduced with a 100 fs jitter limit for the reference clock in the latest PCIe 6.0 specification. As the data rates in high-speed digital designs increase, the limits for overall system jitter become tighter. Due to their high phase noise sensitivity, phase noise analyzers are the instruments of choice for these tests.

Thank You For Your Interest

By clicking ‘Submit’ you agree to our Terms of Use. We take your privacy seriously. For more information please read our Privacy Policy. By registering with All About Circuits you will automatically receive our weekly Product Update and Technology Insider eNewsletters.

Privacy Overview

| Cookie | Duration | Description |

|---|---|---|

| cookielawinfo-checkbox-advertisement | 1 year | The cookie is set by GDPR cookie consent to record the user consent for the cookies in the category "Advertisement". |

| cookielawinfo-checkbox-analytics | 1 year | This cookies is set by GDPR Cookie Consent WordPress Plugin. The cookie is used to remember the user consent for the cookies under the category "Analytics". |

| cookielawinfo-checkbox-functional | 11 months | The cookie is set by GDPR cookie consent to record the user consent for the cookies in the category "Functional". |

| cookielawinfo-checkbox-necessary | 11 months | This cookie is set by GDPR Cookie Consent plugin. The cookies is used to store the user consent for the cookies in the category "Necessary". |

| cookielawinfo-checkbox-others | 1 year | This cookie is set by GDPR Cookie Consent plugin. The cookie is used to store the user consent for the cookies in the category "Others". |

| cookielawinfo-checkbox-performance | 11 months | This cookie is set by GDPR Cookie Consent plugin. The cookie is used to store the user consent for the cookies in the category "Performance". |

| viewed_cookie_policy | 11 months | The cookie is set by the GDPR Cookie Consent plugin and is used to store whether or not user has consented to the use of cookies. It does not store any personal data. |